# Západočeská Univerzita v Plzni

## Fakulta Elektrotechnická

# Katedra Aplikované Elektroniky a Telekomunikací

## **DOCTORAL THESIS**

# Antineutrino detector processing system

Candidate: Ing. Jakub Vlášek

Supervisor: Doc. Dr. Ing. Vjačeslav Georgiev

Pilsen, March 2018

## **Key words**

Inverse beta-decay, DANSS, anti-neutrino, VME, Scintillator, PMT, V1495, S-cube, coincidence

## **Abstract**

This thesis presents a method of data analysis of a multichannel spectroscopic data acquisition system for a large segmented detector of reactor antineutrinos. The method is described, and two implementations are presented. One for PMT based spectrometer for the DANSS detector, built by the Joint Institute for Nuclear Research in Dubna and operating underneath nuclear reactor in the Kalinin Nuclear Power plant and second software based for the S<sup>3</sup> detector, being developed by the Institute of Experimental and Applied Physics of the Czech Technical University in Prague.

## Klíčová slova

Inverzní beta rozpad, DANSS, anti-neutrino, VME, Scintillator, PMT, V1495, S-cube, koincidence

## **Anotace**

Tato práce prezentuje metodu zpracování dat multikanálového systému pro získávání dat z segmentovaného detektoru reaktorových antineutrin. Metoda je popsána a její dvě různé implementace. Jedna pro spektrometr založený na fotonásobičích detektoru DANSS, postavený Spojeným ústavem jaderných výzkumů v Dubně a běží v jaderné Kalininské elektrárně, a druhý, softwarově založený pro detektor S<sup>3</sup>, který je vyvíjen v Ústavu Technické a Experimentální Fyziky ČVUT v Praze.

Ing. Jakub Vlášek 2018

## Prohlášení

Předkládám tímto k posouzení a obhajobě disertační práci zpracovanou v rámci doktorského studia na Katedře aplikované elektroniky a telekomunikací Fakulty elektrotechnické Západočeské univerzity v Plzni. Prohlašuji, že jsem tuto práci vytvořil samostatně, s použitím literatury a zdrojů uvedených v seznamu, který je její neoddělitelnou součástí a za pomoci legálních kopií řádně registrovaného, nebo volně šiřitelného softwarového vybavení. V práci nejsou uvedeny žádné citlivé, či utajované skutečnosti podléhající obchodnímu tajemství, nebo vyžadující speciální režim přístupu. Jakékoli využití a uplatnění uvedených postupů a metod je nicméně možné pouze na základě autorské smlouvy a souhlasu Fakulty elektrotechnické Západočeské univerzity v Plzni.

V Plzni dne 31.8.2018

Ing. Jakub Vlášek

4

## Acknowledgement

I would like to thank my colleagues who helped during work on my thesis. Especially those from the Dzhelepov Laboratory of Nuclear Problems of the Joint Institute of Nuclear Research in Dubna, Russia, the Institute of Experimental and Applied Physics of the Czech Technical University in Prague and Faculty of Applied Electronics and Telecommunications of the University of West Bohemia. I would like to thank namely following people namely: Zdenek Hons, Vjaceslav Georgievich Egorov, Igor Zhitnikov.

I would also like to thank my thesis supervisor Vjačeslav Georgiev and the supervisor-specialist Ivan Štekl.

This research has been funded by the following grants: Czech Technological Agency TE 01020445, Czech Ministry of Education Youth and Sports INGO II – LG14004, Russian State Atomic Energy Corporation ROSATOM 16.1006 and European Regional Development Fund Project No CZ.02.1.01/0.0/0.0/16\_019/0000766.

## Contents

| L | ist of         | abbr                   | eviations                              | 10 |  |  |  |

|---|----------------|------------------------|----------------------------------------|----|--|--|--|

| 1 | Introduction11 |                        |                                        |    |  |  |  |

| 2 | Det            | Detection of neutrinos |                                        |    |  |  |  |

|   | 2.1            | .1 History             |                                        |    |  |  |  |

|   | 2.2            | Che                    | erenkov detection                      | 14 |  |  |  |

|   | 2.3            | Inv                    | erse beta decay detection              | 15 |  |  |  |

| 3 | DA             | NSS                    | Detector                               | 15 |  |  |  |

| 4 | $S^3$          | letec                  | tor                                    | 17 |  |  |  |

| 5 | DA             | NSS                    | spectrometer                           | 21 |  |  |  |

|   | 5.1            | Sig                    | nal path                               | 21 |  |  |  |

|   | 5.2            | CA                     | EN VME-Based Spectrometer              | 22 |  |  |  |

|   | 5.2            | 2.1                    | N625 Quad Linear Analog Fan-In/Fan-Out | 22 |  |  |  |

|   | 5.2            | 2.2                    | N454 Logic Fan In/Fan Out              | 22 |  |  |  |

|   | 5.2            | 2.3                    | V2718 Controller                       | 22 |  |  |  |

|   | 5.2            | 2.4                    | V965 Charge to Digital Converter (QDC) | 23 |  |  |  |

|   | 5.2            | 2.5                    | V1740 ADC Digitizer Card               | 23 |  |  |  |

|   | 5.2            | 2.6                    | V1495 GPIO FPGA Card                   | 23 |  |  |  |

|   | 5.3            | Dat                    | a Acquisition Software                 | 24 |  |  |  |

|   | 5.4            | Dat                    | a event structure                      | 25 |  |  |  |

| 6 | DA             | NSS                    | Firmware Implementation                | 27 |  |  |  |

|   | 6.1            | V14                    | 495                                    | 27 |  |  |  |

|   | 6.             | 1.1                    | V1495 local bus interface              | 28 |  |  |  |

|   | 6.2            | Fir                    | mware framework                        | 29 |  |  |  |

|   | 6.2            | 2.1                    | Build process                          | 29 |  |  |  |

|   | 6.3            | Fir                    | nware building blocks                  | 30 |  |  |  |

|   | 6.3            | 3.1                    | Configuration and status               | 30 |  |  |  |

|                | 6.3.2       | System timestamp               | 31 |

|----------------|-------------|--------------------------------|----|

|                | 6.3.3       | Signal input                   | 31 |

| 6.3.4          |             | Data read-out controller       | 31 |

| 6.3.5<br>6.3.6 |             | Serial communication           | 32 |

|                |             | Output GATE generation         | 32 |

|                | 6.3.7       | Status gate                    | 34 |

|                | 6.4 Fir     | mware cores                    | 34 |

|                | 6.4.1       | Coincidence core               | 34 |

|                | 6.4.2       | Pattern recorder core          | 38 |

|                | 6.5 Gar     | te generator core              | 39 |

|                | 6.6 Fir     | mware resource usage           | 40 |

| 7              | $S^3$ softw | vare coincidence analyzer      | 41 |

|                | 7.1 Sw      | Coinc software description     | 42 |

|                | 7.1.1       | Data input                     | 42 |

|                | 7.1.2       | Data analysis                  | 42 |

|                | 7.1.3       | Data visualization             | 42 |

|                | 7.1.4       | Command and control            | 43 |

|                | 7.2 An      | alyzer software architecture   | 43 |

|                | 7.3 An      | alyzer software class overview | 44 |

|                | 7.3.1       | Config                         | 44 |

|                | 7.3.2       | Log                            | 44 |

|                | 7.3.3       | RootServer                     | 44 |

|                | 7.3.4       | IThread                        | 44 |

|                | 7.3.5       | DataStore                      | 45 |

|                | 7.3.6       | Scheduler                      | 45 |

|                | 7.3.7       | Event                          | 45 |

|                | 7.3.8       | DataSource                     | 46 |

|   | 7.3.9   | DataSink                                             | 47 |

|---|---------|------------------------------------------------------|----|

|   | 7.3.10  | Filter and LambdaFilter                              | 47 |

|   | 7.3.11  | PulseExtractor                                       | 47 |

|   | 7.3.12  | Coincidence                                          | 48 |

|   | 7.3.13  | DataParser and DataParserFactory                     | 48 |

|   | 7.3.14  | Discovery                                            | 50 |

|   | 7.3.15  | Run class                                            | 51 |

|   | 7.3.16  | RunReader                                            | 51 |

|   | 7.3.17  | VBase                                                | 52 |

|   | 7.3.18  | VGraph, VGraphErrors                                 | 52 |

|   | 7.3.19  | VH1D, VH2D                                           | 52 |

|   | 7.3.20  | VTimeGraph                                           | 52 |

|   | 7.3.21  | TimeSeriesHistoGraph                                 | 53 |

|   | 7.3.22  | MultiVH2D                                            | 53 |

|   | 7.3.23  | MultiTimeSeriesHistoGraph                            | 53 |

|   | 7.3.24  | Analyzer and AnalyzerFactory                         | 54 |

|   | 7.3.25  | ADCPrinter                                           | 54 |

|   | 7.3.26  | Scube VME Analyzer (scube_vme)                       | 55 |

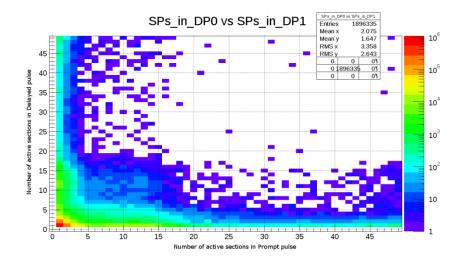

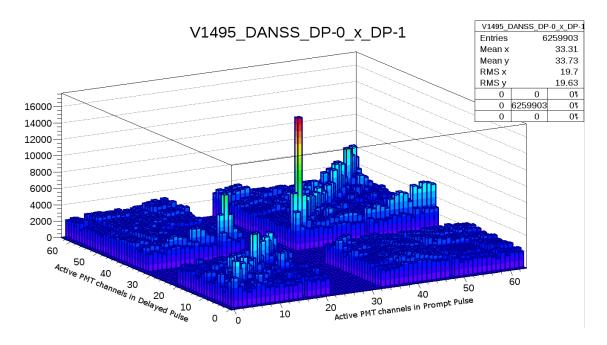

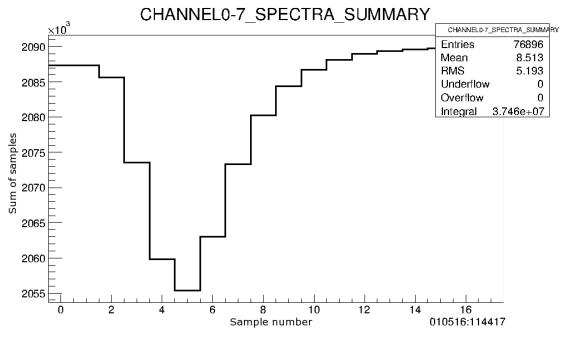

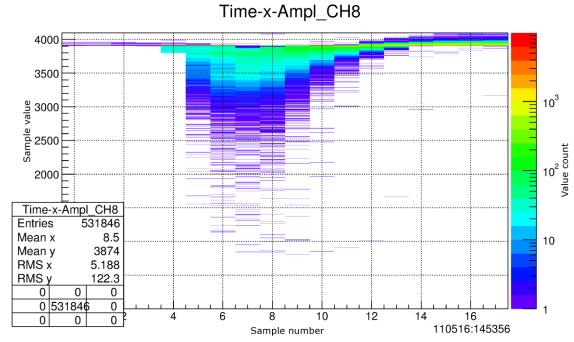

| 8 | DANSS   | Firmware Results                                     | 56 |

|   | 8.1 Dig | gitizer performance results                          | 59 |

|   | 8.2 Co  | mbined spectrometer results                          | 61 |

| 9 | New dat | ta acquisition system proposal – $\mathfrak{A}^3DAQ$ | 64 |

|   | 9.1 Ove | erall architecture                                   | 65 |

|   | 9.2 Typ | pes of supported VME Cards                           | 66 |

|   | 9.2.1   | V1495 with custom firmware                           | 66 |

|   | 9.2.2   | CAEN Digitizer with ADC waveform recording firmware  | 66 |

|   | 9.2.3   | CAEN Digitizer with ODC firmware                     | 67 |

| 9. | 3                | Configuration               | 69 |  |  |  |  |

|----|------------------|-----------------------------|----|--|--|--|--|

| 10 | 0 Conclusions    |                             |    |  |  |  |  |

| 11 | Li               | st of relevant publications | 72 |  |  |  |  |

| 11 | 1.1              | Impacted publications       | 72 |  |  |  |  |

| 11 | 1.2              | Proceedings papers          | 72 |  |  |  |  |

| 12 | Ot               | her results                 | 72 |  |  |  |  |

| 12 | 2.1              | Other impacted publications | 72 |  |  |  |  |

| 12 | 2.2              | Other conferences           | 72 |  |  |  |  |

| 13 | Pr               | ototypes and software       | 73 |  |  |  |  |

| 14 | List of figures  |                             |    |  |  |  |  |

| 15 | List of Listings |                             |    |  |  |  |  |

| 16 | List of Tables7  |                             |    |  |  |  |  |

| 17 | References       |                             |    |  |  |  |  |

## List of abbreviations

FPGA Field Programmable Gate Array

MSPS Mega Samples Per Second

JINR Joint Institute of Nuclear Research (Dubna, Russia)

NPP Nuclear Power Plant

KNPP Kalinin Nuclear Power Plant

ADC Analog to Digital Converter

PMT Photomultiplier Tube

SiMP Silicon Photomultiplier

AFE Analog FrontEnd

DAQ Data Acquisition System

DANSS Detector of reactor AntiNeutrinos based on Solid Scintillator

VME Versa Module Europa bus

QDC charge(Q) to Digital Convertor

IBD Inverse Beta Decay

WLS Wavelength shifting

DPP Digital Pulse Processing

## 1 Introduction

Neutrinos are a hot topic of contemporary particle physics and their study is a subject of a great interest. Initially, it was assumed that neutrinos are mass-less, however, a discrepancy between the theoretically predicted solar neutrino flux with ground measurements (the "Solar Neutrino Problem" [1]) led to the discovery that neutrinos do have mass and can oscillate between their flavors (electron, tau, muon).

There are three major sources of neutrinos – sun, particle accelerators and nuclear reactors.

The high intensity of neutrino flux generated by nuclear reactors provides a good opportunity to study the elementary behavior of neutrinos. There are experiments, including the RENO (Reactor Experiment for Neutrino Oscillations) [2], which attempt to measure neutrino oscillations with detectors spaced hundreds meters from the reactor. But the amplitude of the neutrino oscillations is a question. Therefore, it is necessary to place the detector as close to the reactor as possible. Unfortunately, existing detectors are mostly based on hydrogen-rich liquids, such as kerosene, which pose a flammable hazard, an unacceptable for a reactor building.

One of the possibilities to avoid the fire hazard and gain access close to the reactor from the power plant operators is to use polystyrene scintillating detectors. This has been used by the DANSS (Detector of reactor AntiNeutrinos based on Solid Scintillator) detector [3], operated by the Joint Institute of Nuclear Research in Dubna and the Institute of Theoretical and Experimental Physics in Moscow. This 1m<sup>3</sup> detector, made from 2500 scintillating polystyrene 1×4×100 cm<sup>3</sup> bars coextruded with Gadolinium layer has been running for two years in a close proximity to the core of the Kalinin NPP. It is mounted in a z-axis moveable platform (8-12m) to explore the short-range neutrino oscillations.

Together with Dzhelepov Laboratory of Nuclear Problems (DLNP) of JINR, the Institute of Experimental and Applied Physics of Czech Technical University Prague are currently constructing a new anti-neutrino detector –S<sup>3</sup> as an evolution of the DANSS design.

S<sup>3</sup> is a smaller detector with a volume of 0.4×0.4×0.4 m<sup>3</sup> consisting of 80 scintillating plates with improved light yield. At present, there are two detectors prototypes under construction. One detector will be placed next to the DANSS experiment in KNPP to provide reference information about the nuclear reactor power level. The second is expected to be placed in the Temelín NPP. Both nuclear power plants are of the same VVER-1000 technical specification.

The DANSS Data acquisition system is based on hardware triggered CAEN charge convertors (QDCs) and is controlled by logic implemented in an Field Programmable Gate Array. The S<sup>3</sup> DAQ is based on self-triggered CAEN multichannel ADC. The data reduction is implemented in software on a PC.

The aim of this thesis is to:

- prepare and design the detection algorithm of the DANSS detector

- design and implement the algorithm as a FPGA firmware for DANSS

- design and implement active cosmic veto FPGA firmware for DANSS

- design and implement the algorithm for the S<sup>3</sup> detector

The method must detect the inverse beta decay process  $\tilde{v} + p \rightarrow e^+ + n$ , where antineutrino  $\tilde{v}$  reacts with a proton p and produces positron  $e^+$  and neutron n.

This thesis is divided into the introduction, eight chapters and the conclusions. The second chapter briefly describes the way neutrinos are detected. Chapters 3 and 4 describe the DANSS and S<sup>3</sup> experiments.

The author's involvement begins with chapter 5, where the DANSS data acquisition system is described in detail. Chapter 6 describes the FPGA firmware newly developed for the DANSS DAQ.

Chapter 7 describes the C++ software implementation of an application capable of online experiment monitoring, visualization, analysis and the inverse beta decays signature detection.

Chapters 8 provides results of technical measurements obtained during the commissioning of the DANSS detector in the KNPP.

## 2 Detection of neutrinos

Neutrinos are particles which have very small probability of interaction (cross-section) with ordinary matter. Therefore, the detectors have to be either very large (kilometer scale), as is the case for detection of cosmic neutrinos or very close to a source of neutrinos, e.g. a nuclear reactor. There are two methods of their detection, using Cherenkov radiation and using inverse beta decay detection.

## 2.1 History

A hypothetical particle, electrically neutral and having mass smaller than that of the proton was first proposed by Wolfgang Pauli in 1930 [4]. In 1933 Enrico Fermi named it a "neutrino" to distinguish it from the newly discovered neutron [5].

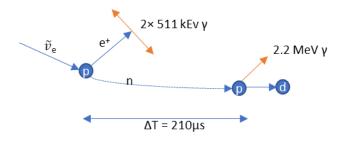

At first, neutrinos were considered massless. Their first detection was done by F.Reines and C.Cowan [6] using nuclear reactor as a strong source of antineutrinos using inverse beta decay. They used a liquid scintillator where the electron antineutrino interacts with a proton, emitting a positron and a neutron. The positron annihilates creating two 511 kEv gamma photons and the neutron is captured by a proton creating a deuteron and emitting gamma rays with energy of 2.2 MeV (Figure 2-1).

Figure 2-1 Inverse beta decay in a liquid scintillator

Several experiments with solar (R. Davis et al [7]), atmospheric, accelerator and reactor neutrinos have provided the existence of neutrino oscillations driven by non-zero masses and neutrino mixing. Neutrino oscillation is a quantum mechanical phenomenon whereby a neutrino created with a specific lepton flavor (electron, muon, tau) can later be measured to have a different flavor. The probability of measuring a particular flavor for a neutrino varies between 32 known states as it propagates through space. The neutrino oscillations were first predicted by Bruno Pontecorvo in 1957 [8], [9], [10].

Since neutrinos are massless in standard model of electroweak interactions, this verification of neutrino oscillations (and therefore mass) was first strong evidence for physics beyond the

standard model. This convincing evidence for neutrino oscillations has been confirmed by other experiments (SNO [11], RENO [2], Daya Bay [12]). Neutrino oscillations experiments are not sensitive to the nature of the neutrino mass and give no information on the absolute neutrino mass scale [8].

Neutrino oscillation is a function of the ratio L/E where L is the distance travelled and E is the neutrino energy. To measure neutrino oscillation for different distances from the source is an important task. Also, several experiments announced the reactor anomaly [13], which can be explained by existence of sterile neutrinos. These questions can be solved by detector of neutrinos located as close as possible to the nuclear reactor [5].

#### 2.2 Cherenkov detection

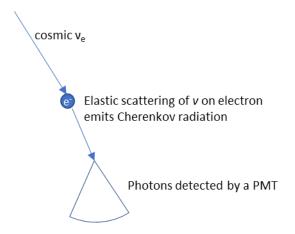

The interaction of a high energy cosmic neutrino in the detector volume produces electrically charged particle which travels faster than the local speed of light while emitting Cherenkov radiation. The photons are then detected by sensitive light detectors - photomultipliers. The particle track can be then reconstructed from the times of arrival of the Cherenkov photons.

Figure 2-2 Principle of high energy neutrino detection

Currently, there are several such detectors either operating or being built in the world.

- Super-Kamiokande operational, 40 m steel tank with ultrapure water [14]

- Ice-Cube operational, South Pole observatory using about cubic kilometer of Arctic ice as detector volume [15]

- Baikal Gigaton Volume Detector under construction, 1 km<sup>3</sup> of clean Russian lake

Baikal water [16], [17]

- ANTARES/KM3NeT operational, 1km<sup>3</sup> of Mediterranean sea [18]

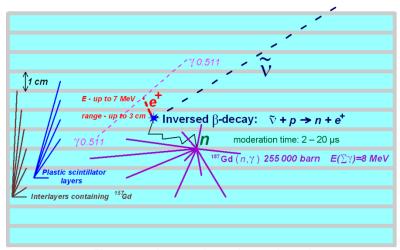

#### 2.3 Inverse beta decay detection

The IBD detection method is used mostly in detectors of reactor neutrinos. The antineutrino interacts with a proton producing a positron and a neutron. The positron immediately annihilates with emission of two gamma rays of 511 keV each. The neutron is thermalized by collisions with light nuclei and captured. Neutron capture by Gadolinium emits several gamma rays with the total energy of 8 MeV. The IBD method looks for the characteristic signature of annihilation and following spatially close gamma rays of the neutron capture.

### Experiments based on IBD include

- Daya-Bay [12] Eight 20 ton kerosene based antineutrino detectors in three locations within 2 km of six nuclear reactors in Daya Bay, China

- DANSS [3]—1 cubic meter polystyrene based detector about 10 m from the nuclear reactor in the Kalinin nuclear power plant, Russia.

#### 3 DANSS Detector

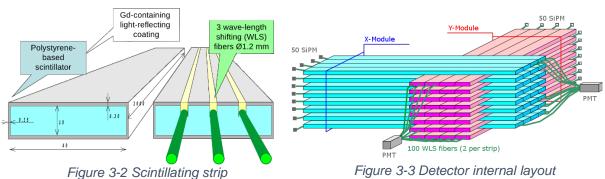

The detector is constructed from 2500 scintillating strips with dimensions of  $4\times1\times100$  cm. Each strip is coated by a reflexive layer containing Gadolinium (Figure 3-2) and contains wavelength shifting fibers for light collection.

Figure 3-1 DANSS Team members with the detector in the KNPP technical room [3].

Each successive layer of the detector is built perpendicularly to the previous one. Ten parallel layers of 5 neighboring strips form one detector section (module - Figure 3-3). The X and Y sections are intercrossing so that the positional information of the interaction can be extracted. Every detector section is connected to one PMT.

The light is collected through wavelength shifting fibers by PMT and MPPCs. Each bundle of 100 WLS fibers from 50 strips is connected to one PMT. The average yield from single strip of is about 35 photoelectrons per 1 MeV [3].

Figure 3-3 Detector internal layout

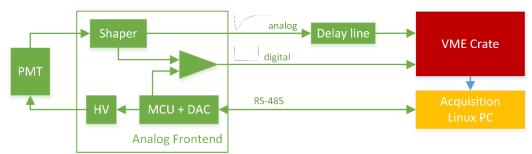

Every PMT is connected to an analog frontend (AFE) containing the high voltage power supply, pulse shaper, analog comparator and controlling MCU with a DAC. All AFEs are controlled from the acquisition PC via RS-485 bus. The output pulse from the pulse shaper is about 100 ns long and is accompanied with above-set-threshold digital pulse.

The MPPCs are connected to a separate data acquisition system which is not a subject of this thesis.

The DANSS detector uses the inverse beta decay as its detection principle (Figure 3-4). The electron antineutrino coming from the reactor core interacts with a proton inside the scintillator and produces positron and a neutron. The positron annihilates and creates a characteristic pair of 511 keV gamma rays – "prompt signal". After 2 to 20 us the neutron moderates and is captured by Gadolinium. The resulting gamma rays have a total energy of 8 MeV and should be detected within a sphere of about 20 cm from the original neutrino interaction - "delayed signal". This method of detection was verified by small scale DANSS detector demonstrator DANSSino [19].

Figure 3-4 Inverse beta decay detection

Thanks to the segmented nature of the detector and the way the strips are placed, the IBD produces a characteristic signature which can be searched for. Therefore, the data acquisition system must be able to register a coincidence of two events separated by few microseconds. Generally, both prompt and delayed signals can come from the same PMT channel. The DAQ must be sufficiently responsive so that the delayed signal does not fall within the dead time.

Additionally, the DANSS detector is using cosmic muons with vertical tracks for calibration purposes and the DAQ must also record them.

## 4 S<sup>3</sup> detector

The  $S^3$  detector project is a result of cooperation between DLNP JINR and IEAP Prague. Its main goal is the improvement of the energy resolution by optimizing the scintillating elements. The detector will be placed next to the DANSS detector in the Kalinin NPP and possibly in the Temelin NPP in the Czech Republic. The Czech contribution is being funded by a grant of the Czech Technological Agency TE 01020445 – CK RANUS.

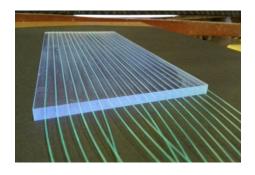

Figure 4-1 S3 scintillating plate with WLS fibers

The S³ detector consists of 80 20×40×1 cm plates (Figure 4-1) manufactured by the NUVIA Group placed in a X-Y pattern like the DANSS detector. The plates contain 19 grooves for WLS fibers collecting light. In contrast with the DANSS strips, the plates are not co-extruded with reflective and Gadolinium bearing coating, but manually wrapped in Teflon tape, as the co-extrusion process thermally changes the properties of the scintillator. Low density polyethylene foils doped with 10%<sub>wt</sub> Gd<sub>2</sub>O<sub>3</sub>, manufactured by the Institute of Macromolecular Chemistry (IMC) of Czech Academy of Sciences, are placed between the plates. The light from each individual plate is sensed by SiPM and amplified by an analog frontend.

Figure 4-2 S<sup>3</sup> detector schematic

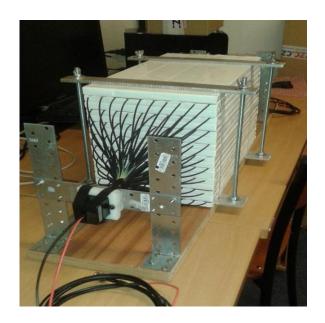

To understand properties of the detector a prototype called S-cubino was constructed (Figure 4-3). It consists of 18 plates divided into two interleaved groups connected to two Hamamatsu R7600U-300 PMTs.

Figure 4-3 S-cubino detector

It is shielded by a 10-cm layer of hundred years old lead (for low internal radioactivity) to shield from gamma radiation, 8 cm of polyethylene for thermal neutron shielding and 8 cm of borated polyethylene for fast neutron shielding.

Figure 4-4 Construction of the scubino detector

Initial measurements with the S-cubino detector were made in the building of the Faculty of Mathematics and Physics of the Charles University in Troja in Prague and then the detector was moved into the underground shelter Bezovka in Prague.

The full detector is being constructed as of spring 2018 in the IEAP CTU for testing. All 19 WLS fibers are connected to one SiPM.

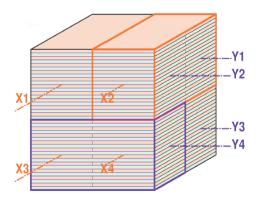

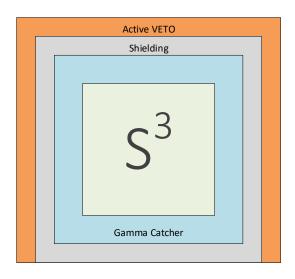

In Russia, the second S<sup>3</sup> detector prototype, in parallel development, prototype is being constructed. It will also consist of 80 scintillating plates, but will have use traditional PMTs for light collection. In addition, the detector will have a "gamma catcher" scintillating plates (5x50x100 cm) around the active detector to catch gammas generated inside the detector. As with the DANSS detector there will be active veto system to detect the fast neutron background events mimicking the IBD signature. Together, the detector will have 80 PMT per-plate channels, 16 bigger PMTs connected to the second scintillating side, 8 gamma catcher channels and 16 active veto channels totaling 120 channels to be sampled by the data acquisition system.

Figure 4-5 S<sup>3</sup> Detector layout, Russian version

The schematic layout of the S<sup>3</sup> detector is shown on Figure 4-5. Figure 4-6 shows the start of the prototype construction with one gamma catcher scintillator placed between lead shielding.

Figure 4-6 Gamma catcher scintillator

## 5 DANSS spectrometer

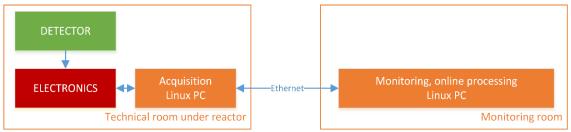

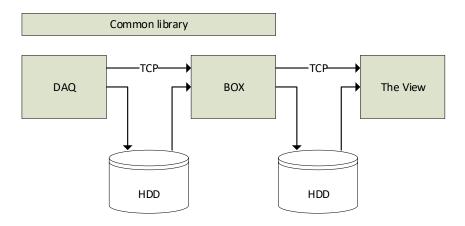

The data acquisition system is installed together with the DANSS detector assembly in a technical room underneath the reactor. Since the room is inside controlled-access part of the nuclear powerplant, the DAQ is connected via fiber optic ethernet connection to a control room (Figure 5-1).

Figure 5-1 Overall system schematics

The acquisition PC collects data from the measurement electronics and saves them onto a disk. Monitoring PC connects to the DAQ via TCP connection for online monitoring of the detector by on-duty personnel. There is no outside connection out of the monitoring room, therefore acquired data can to be only transferred from the powerplant using an approved (by KNPP) USB Flash drive.

## 5.1 Signal path

Every PMT channel has its individual analog front-end electronics which is placed inside the detector shielding. A ribbon cable carries configuration RS-485 bus and power for the AFEs. The RS-485 is connected via an interface box to the acquisition PC. The AFE provides a configurable high voltage source for the photomultiplier and control voltage for above-threshold digital trigger comparator. Pulse shaper lengthens and amplifies the pulses so they can be captured by the electronics. Since the trigger logic has a propagation delay, it is necessary to delay the analog signals using a delay line (coax cable with 80 ns t<sub>pd</sub>).

Figure 5-2 PMT Signal Path

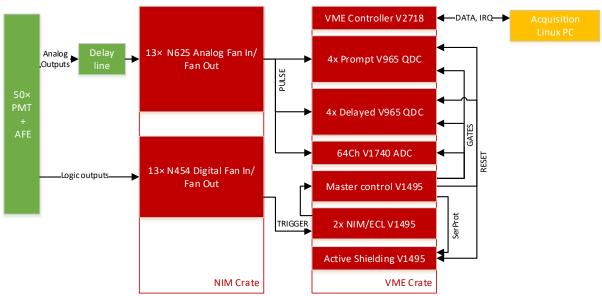

#### 5.2 CAEN VME-Based Spectrometer

Overall schematics of the PMT spectrometer are shown in Figure 5-3. The spectrometer is installed in three NIM crates and one VME crate. NIM crate is used for signal fan-out and the VME crate for the spectrometer itself. The spectrometer consists of signal acquisition modules (QDC, ADC, FPGA), control (FPGA) and conversion (FPGA). The author of this thesis has been responsible for the development of the firmware for the FPGA V1495 modules. Hardware of the spectrometer is composed of several modules mentioned below.

Figure 5-3 Hardware schematics

#### 5.2.1 N625 Quad Linear Analog Fan-In/Fan-Out

The CAEN N625 has 4 groups of 4 analog summed inputs with 4 analog outputs each. This card is used to branch the analog signals from AFEs to Prompt, Delay QDCs and the ADC. For 50 channels, 13 such cards are required.

#### 5.2.2 N454 Logic Fan In/Fan Out

CAEN N454 has 4 groups of NIM logic digital OR-ed inputs with four direct outputs and two negated outputs. It is used for as a signal repeater and a fan-out for debug purposes.

#### 5.2.3 V2718 Controller

The CAEN V2718 VME Controller serves as a bridge between the VME crate bus and a Linux PC with DAQ software. It is connected via a multimode optical fiber link. The VME cards are addressable by 32-bit address, where the first 16 bits are set by either by a rotary switch (VME64 crates) or slot position (VME64X crates). The VME64 bus has bandwidth of

80MB/s. The VME bus supports single read/write, burst 4KB block (BLT) and chained burst (CBLT) accesses modes. The chained block access mode uses a multicast target address which is set for a group of similar adjacent cards. The CBLT is used for reading data from the V965 QDCs. The VME Bus has also 8 IRQ lines, the V2718 bridges them to a PC IRQ.

## 5.2.4 V965 Charge to Digital Converter (QDC)

The 16-input charge to digital converter integrates the charge on input channels during active level-sensitive GATE signal and converts it using 12 bit ADC and creates an data event accessible via the VME bus. Each channel is converted twice, once with gain of  $1\times$  and once with gain of  $8\times$ . The GATE signal must precede the analog input by at least 15 ns [20]. The conversion of all channels takes 5.7  $\mu$ s, with a total dead time of 6.9  $\mu$ s.

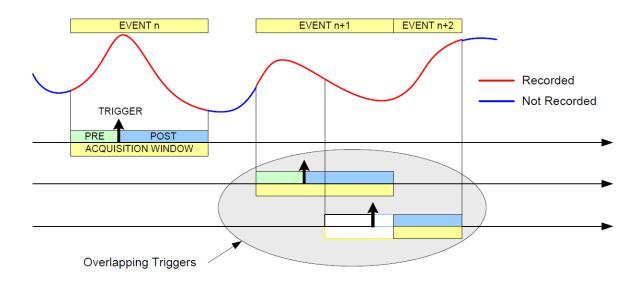

#### 5.2.5 V1740 ADC Digitizer Card

CAEN V1740 is a 64-input 12 bit 62.5 MSPS simultaneous analog to digital converter with a 2  $V_{pp}$  input range. It has a 192k samples per channel memory buffer, which can be divided into up to 1024 separate events (of 192 samples each). The digitizer can be triggered either internally by any channel exceeding a threshold voltage, or externally via an edge-sensitive GATE signal. After a trigger, all enabled channels are sampled and stored to event buffer. Additional triggers during the acquisition window can be either ignored or cause the acquisition to be prolonged (trigger overlapping mode). The digitizer operates without a dead-time. That is, another event can be acquired as soon as previous ends without any delay.

#### 5.2.6 V1495 GPIO FPGA Card

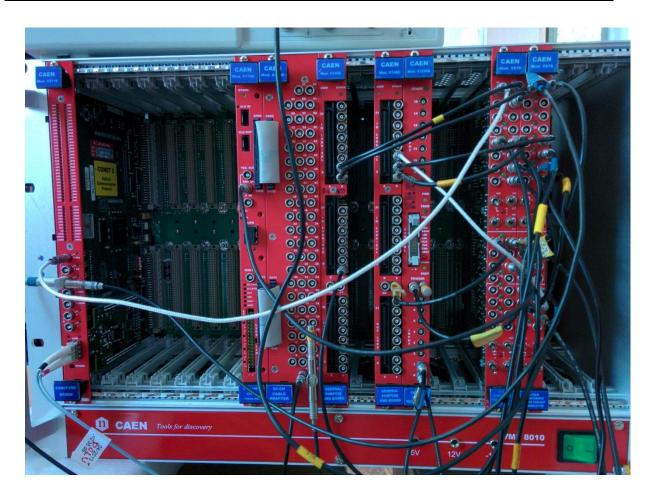

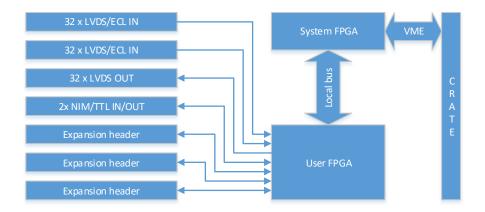

CAEN V1495 is a VME card with an empty user-programmable Altera Cyclone I EP1C20 FPGA with 20K Logical Elements and 36 KiB on-chip ram. The card provides two 32 channel LVDS/ECL/PECL high-density (3M P50E-068-P1-SR1-TG) inputs, one 32 channel LVDS outputs, 2 LEMO NIM/TTL inputs/outputs and one LED. Additionally, three add-on slots are available, which can be filled by 32-channel LVDS/ECL/PECL inputs, 32-channel LVDS output, 8-channel NIM/TTL LEMO input/output daughter cards.

Figure 5-4 Development VME Crate

#### 5.3 Data Acquisition Software

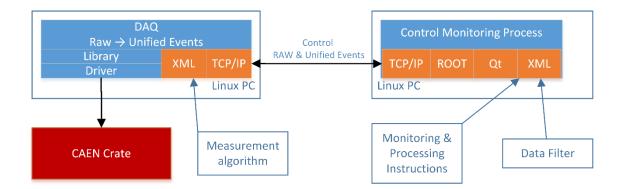

The spectrometer data are collected, monitored and partially on-line processed by a system described in detail in [21]. It is a system running on a Linux PC. An interesting feature of the system is that not only the vendor-specific raw data from the VME modules are written to the disk, but the system also translates them into a unified data(u-data) format formed by a tuple (channel\_id; value) hiding the complexity and variability of the specific hardware. It also allows on-line calculation of areas (charges) of pulses. That allows creation of data processing programs universally usable for differently configured crates. Both raw and u-data are available for remote access via TCP/IP and so is program control. Figure 5-5 shows the overall DAQ schematics. The measurement-specific acquisition algorithm is described using an XML based language containing sections appropriate for different phases of the measurement (crate initialization, start, IRQ handling operations, end and data storage). The DAQ also contains an Qt/ROOT-based application allowing for on-line status monitoring.

Figure 5-5 DAQ System Architecture

#### 5.4 Data event structure

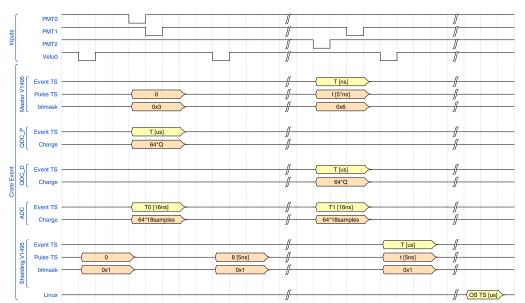

Figure 5-6 shows simplified example of inputs together with the output data structure of the DAQ event. Each input pulse is identified by its relative timestamp(TS), collected charge from both ADC and QDC and a bit mask of associated active shielding veto events.

Figure 5-6 DAQ Crate event structure

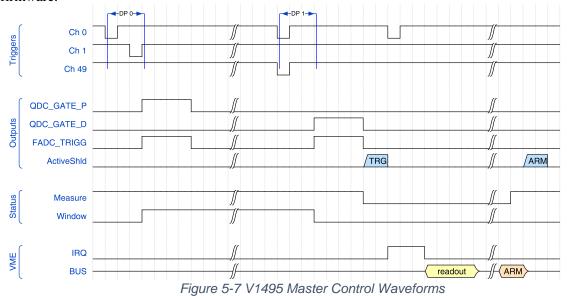

Figure 5-7 shows the responses of the control FPGA to example trigger inputs. The firmware sends enabling GATE signals to appropriate prompt and delayed QDCs, ADCs and the active shielding FPGA firmware.

## 6 DANSS Firmware Implementation

The development of the FPGA firmware for the V1495 cards of the DANSS PMT spectrometer has been the responsibility of the author of this thesis.

The final configuration of the spectrometer requires the V1495 in 4 roles served by different firmware variations:

- master crate measurement control

- active shielding pattern recorder

- pattern generator.

- NIM/LVDS translator

The master measurement control firmware monitors incoming above-threshold pulses from PMT AFEs and if a configured pattern is observed, sends GATE signals to appropriate QDCs, ADC and the active shielding pattern recorder.

The pattern recorder firmware continuously samples above-threshold pulse outputs of the shielding scintillators and stores events inside a circular buffer with their relative timestamps.

The NIM/LVDS translator is a simple logic level translator.

Pattern generator firmware generates configurable pulses used for testing of the entire data acquisition system.

However, because the functionality can be useful in other experiments, the firmwares have been designed with as much run-time configurability via the VME bus as possible and there is no hardcoded configuration.

## 6.1 V1495

The firmware is designed for the user FPGA of the CAEN V1495 card used in the spectrometer. V1495 contains a CAEN-programmed system FPGA and an empty 20K LE Cyclone I chip.

The system FPGA interfaces the VME bus, contains 256 32-bit word data readout FIFO and can assert configured VME IRQ line and maps VME read/write accesses to a local bus. User FPGA is connected to 195 user I/O. Schematic diagram is shown in Figure 6-1.

Figure 6-1 V1495 schematic diagram

#### 6.1.1 V1495 local bus interface

The signals used between the system and user FPGAs are shown in Table 6-1. The bus supports single read, single write and burst (BLock Transfer - BLT) read. The local bus supports only 32-bit word VME access mode.

| Signal name | Direction | Width [bits] | Description                      |

|-------------|-----------|--------------|----------------------------------|

| nRESET      | in        | 1            | System reset                     |

| CLK         | in        | 1            | 40 MHz system clock              |

| nADS        | in        | 1            | Start of Address Data Cycle      |

| nBLAST      | in        | 1            | Terminate transfer               |

| WnR         | in        | 1            | Write or Read                    |

| nREADY      | out       | 1            | Output data ready or BLT request |

| LAD         | inout     | 16           | Bidirectional data/address bus   |

| nIRQ        | out       | 1            | Interrupt request                |

Table 6-1 V1495 local bus signals

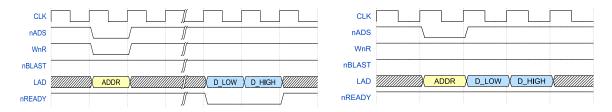

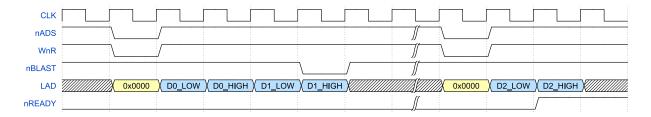

Single read and write cycles start with the system FPGA deasserting the nADS signal and placing 16-bit address on the bus. In the single read (Figure 6-2) bus cycle the system FPGA waits until the nREADY signal is deasserted. In the single write (Figure 6-3) cycle data follows the address immediately.

Figure 6-2 Local bus read cycle

Figure 6-3 Local bus write cycle

The BLT transfer is used to transfer event data from the user FPGA to the system FPGA FIFO for data readout. The cycle begins with the user FPGA deasserting the nREADY signal

and the system FPGA performing read access to address 0x0000. If the system FIFO becomes full, nBLAST is deasserted and the transfer is interrupted.

Figure 6-4 Local bus BLT cycle

#### 6.2 Firmware framework

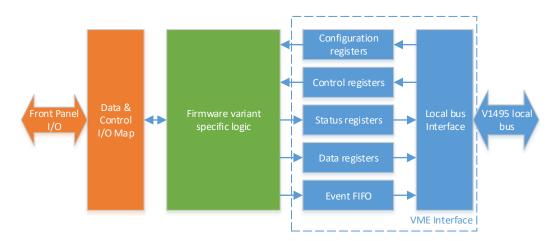

It was impossible to fit all the required roles in one firmware due to the small size and performance of the user FPGA. Therefore, a modular approach to development was used. Each firmware variant is built from a common code base and contains a shared VME interface part, variant-specific part and external signal routing (Figure 6-5).

Figure 6-5 Firmware framework structure

#### 6.2.1 Build process

The firmwares are generated from single Quartus project using revisions. Each firmware has its separate revision. Project source code is stored in a git repository. The build process uses external Makefile.

At the beginning of compilation a pre-flow TCL script generates a VHDL file containing the revision name and revision version in the format of YYMMDDcc, where cc is the number of git commits made on the build day. These constants can be read from the firmware via the VME bus to verify used variant and revision of the source code used. A post-flow script converts the firmware bitstream to the required RBF format and renames the output file to reflect the variant name and revision.

After the compilation finishes, make executes a ModelSim testbench which generates a list of all available configuration registers and their default values. The list is then converted to XML format used by the DAQ software and VHDL for testbench creation.

### 6.3 Firmware building blocks

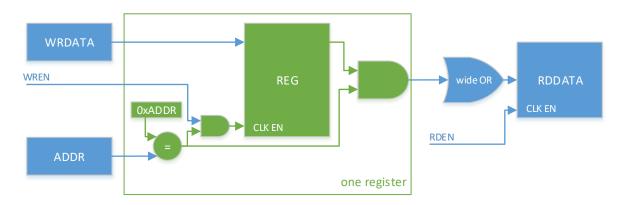

#### 6.3.1 Configuration and status

The configuration and status block implements VME-accessible 32-bit registers. Each register can be set to either read, write or read/write access. The logic circuit used is shown in Figure 6-6. VHDL implementation of procedure is shown in Listing 6-1 and their example use in Listing 6-2.

Figure 6-6 Configuration registers schematics

```

procedure reg(raddr : unsigned;

-- register address

variable regval : inout unsigned; -- register variable

racc : reg_t;

-- register access (r, w, rw)

-- documentation: (cfg / stat)

purpose : purpose_t;

pgroup : natural;

-- documentation: group

gtype : gatetype_t;

-- documentation: type of gate

name : string;

-- documentation: name

-- documentation: description

desc : string;

values : string

-- documentation: possible values

) is

variable isaddr : std_logic;

: std_logic_vector(regval'range);

variable tmp

begin

-- synthesis translate off

print_reg(raddr, std_logic_vector(regval), racc, purpose, pgroup,

gtype, name, desc, values, "unsigned", regval'length,

"D32"); -- used by ModelSim in the build flow

-- synthesis translate on

if racc = r or racc = rw then

isaddr := '0';

if addr = raddr then

isaddr := '1';

end if;

tmp := std_logic_vector(regval) and (regval'range => isaddr);

-- rd is a process-wide variable

rd(regval'range) := rd(regval'range) or tmp;

end if;

```

Listing 6-1 VHDL implementation of registers

Listing 6-2 Example use of register

#### 6.3.2 System timestamp

A 32-bit counter running at the core frequency (200 MHz) is used for timestamp of data events. A clock divider (default is 1  $\mu$ s) and its overflow period can be configured. It is possible to reset the system timestamp either using the serial protocol or a dedicated edge-sensitive time synchronization input.

#### 6.3.3 Signal input

Above-the-threshold signals are synchronized to the 200 MHz core clock domain and configurable signal edge is detected. A de-glitch filter is applied to ignore any additional edges within configured time. Output of this block is an edge signal asserted for one core clock cycle.

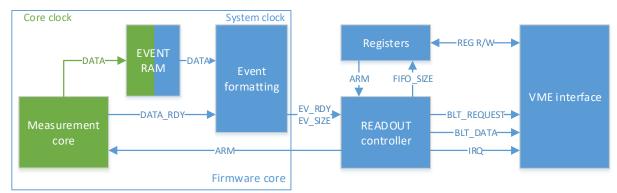

#### 6.3.4 Data read-out controller

Data read-out block controls the measurement. After reset, it is initialized to a standby IDLE state. A register write to the ARM register starts the measurement. The read-out controller waits until assertion of EVENT\_READY signal from the firmware core. Then it requests a BLT transfer from the system FPGA and after its completion, an IRQ is asserted. It is possible to delay the IRQ request using a settable timer to allow other VME crate modules to finish their processing. The readout controller then either waits for another write to the ARM register or rearms the system automatically, after a settable timer.

The size of the event transferred to the system FPGA FIFO is tracked and available for reading. If the FIFO is full, automatic rearms are blocked. Reading the FIFO\_SIZE register resets it. Thus, the read-out cycle from the point of view of the DAQ is as follows:

#### 1. Write 1 to ARM register

- 2. Wait for IRQ

- 3. Read FIFO\_SIZE register

- 4. Block transfer from the V1495 card

Figure 6-7 Data readout schematics

The relationship of the readout controller to other modules is shown in Figure 6-7.

#### 6.3.5 Serial communication

The V1495 does not allow the user firmware to request a transfer on the VME bus, therefore any communication between two V1495 cards must be performed via the front-panel I/O. A simple pulse width modulation is used. The Table 6-2 lists all currently implemented commands.

| Command  | Pulse Length<br>[5 ns] | Accepted length [5 ns] | Description                     |

|----------|------------------------|------------------------|---------------------------------|

| SAMPLE   | 2                      | 1 – 3                  | Detector pulse                  |

| WIN_FAIL | 5                      | 4-6                    | Coincidence window unsuccessful |

| WIN_OK   | 8                      | 7-9                    | Coincidence window successful   |

| ARM      | 11                     | 10 – 12                | Re-ARM                          |

| TIMESYNC | 14                     | 13 – 15                | System TS overflow              |

| RESET    | 23                     | 22 – 24                | System reset                    |

Table 6-2 Serial protocol commands

## 6.3.6 Output GATE generation

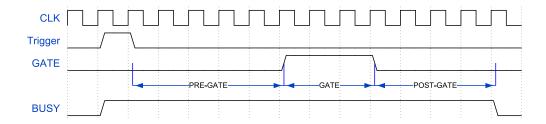

### 6.3.6.1 Single gate

The single output gate generates a level-active signal of configurable polarity which has a programmable pre-gate wait, gate and post-gate duration as shown in Figure 6-8. The GATE signal is routed to the V1495 front-panel I/O and the BUSY signal can be used internally in the firmware core.

Figure 6-8 Single GATE timing diagram

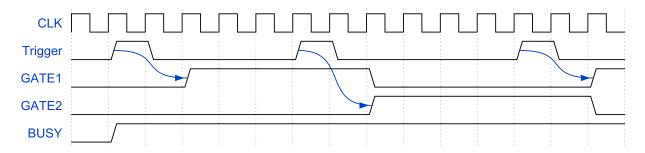

#### 6.3.6.2 Dual alternating gate

The dual alternating gate has two outputs, GATE1 and GATE2. It can operate in two modes, latency hiding and always alternating. In the latency hiding mode the GATE2 is used for output gates only if the GATE1 output is already busy (Figure 6-9) and not currently generating active gate signal. A configurable timer can lengthen the time the other channel is blocked after the end of active gate signal.

Figure 6-9 Alternating gate - Latency hiding mode

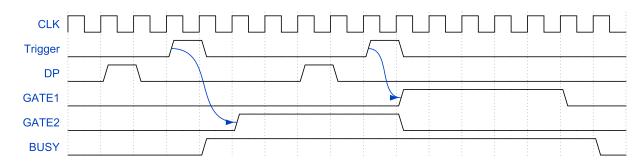

In the always alternating mode (Figure 6-10), additional input DP (Detector Pulse) is used to switch between gate outputs.

Figure 6-10 Alternating gate - Always alternating

The dual gate can be also configured to swap output channels, generate output in both channels at once and to stop generating pulses after two triggers (until system RE-ARM).

#### 6.3.7 Status gate

Monitoring of internal status of the firmware is possible using the status gate. It is configured using a bitmask register. The output is either selected level-active internal signal or an edge-sensitive signal lengthened using the single output gate. Table 6-3 lists available output signals.

| Type                                   | Value                              | Description                                                      |

|----------------------------------------|------------------------------------|------------------------------------------------------------------|

| edge                                   | 0x1                                | Any detector pulse                                               |

|                                        | 0x2                                | Recorded detector pulse                                          |

|                                        | 0x4                                | Successful coincidence window                                    |

| 0x8 Unsuccessful coincidence window    |                                    | Unsuccessful coincidence window                                  |

| 0x10 System RE-ARM                     |                                    | System RE-ARM                                                    |

|                                        | 0x20                               | External time synchronization                                    |

|                                        | 0x40                               | System timestamp overflow                                        |

| level                                  | 0x100                              | System measuring (i.e., not dead-time)                           |

| level 0x200 System is in the RUN state |                                    | System is in the RUN state                                       |

| level                                  | level 0x400 IRQ signal is asserted |                                                                  |

| level                                  | 0x800                              | Measurement window open                                          |

| level                                  | 0x1000                             | Waiting for DAQ (active between IRQ assertion and ARM reception) |

Table 6-3 Status signals

#### 6.4 Firmware cores

#### 6.4.1 Coincidence core

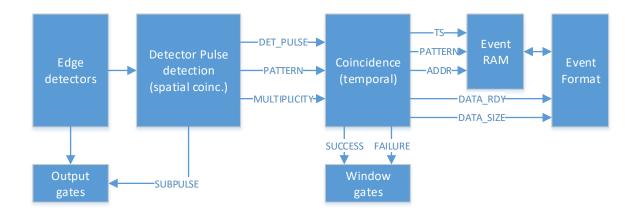

The coincidence core implements the temporal coincidence of spatial coincidences of 64 input channels operating at 200 MHz (5 ns sampling time). Whenever an edge is sensed at the input, a small (~100 ns) detector pulse coincidence window opens and captures trigger pattern occurring in the detector. Its purpose is to capture a single physical interaction in the detector which was due to the varying propagation delays in the detector and analog electronics chain captured at different clock edges. The DP opens a main coincidence window (~ 100 μs). If the coincidence conditions are met, an event is generated. The event contains a coarse system timestamp and a list of detector pulses with their channel patterns and fine timestamp relative to the main coincidence window start. Schematics of the module are shown in Figure 6-11.

Figure 6-11 Coincidence master schematics

#### 6.4.1.1 Coincidence core modules

The DP spatial coincidence module opens a coincidence window whenever any edge detector asserts a single clock pulse. For the duration of the window, the 64-bit input vector pattern is logically summed. The module also counts the number of ones in the vector. After the window closes, the module asserts the DET\_PULSE signal to the main coincidence module together with its 64-bit pattern and multiplicity (i.e. the number of ones in the vector). A dead-time after the window end can be set to disable inputs for configured time.

The main coincidence module operates in two different modes – **fixed and dynamic window**. In fixed window mode, the coincidence window always lasts the configure time and at the end the window is considered as successful if the number of pulses is either within configured range (minimum and maximum) or a multiplicity of any pulse is higher than configured. In the dynamic mode, the window ends as soon as the minimal number of pulses or multiplicity is recorded. Each pulse pattern and its relative timestamp is stored in the Event RAM. A counter keeps track of the total number of detector pulses observed between two successful coincidence windows. This allows the DAQ to calculate the ratio between recorded pulses and total pulses of the detector (i.e. the detection efficiency).

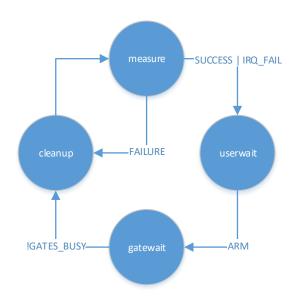

Figure 6-12 Coincidence master measurement state machine

The measurement is controlled by a state machine (Figure 6-12). The *measure* state waits until the main coincidence window finishes. Successful window results in the shared data readout module notification. A configuration option is present to generate IRQ even in case of coincidence window failure (used when there is a need to programmatically clear some other block in the VME crate). In the *userwait* state the machine waits for the DAQ to send the ARM command. The *gatewait* state waits until all output gates are completed. In the *cleanup* state all gates are reset and the state machine transitions back to *measure* state after 2 clock periods.

#### 6.4.1.2 Coincidence core outputs

The coincidence core can be generated with two kinds of output gates — eight 8:1 single gates or four 16:1 dual alternating gates. For the 8:1 single gates, inputs 0 to 7 are mapped to first output channel, 8 to 15 to second and so on. Similarly, channels 0 to 15 are mapped to the first output dual alternating gate. If the always alternating mode is enabled, like in the DANSS spectrometer, the 4 output gates act effectively as one dual output alternating gate.

The core contains one single gate triggered by coincidence window success, one for coincidence window failure and 8 independent configurable status gate outputs.

If enabled, the core is generated with the serial protocol master for control of slave modules (the active shielding pattern recorder).

#### 6.4.1.3 Coincidence core event format

The format of the event (Table 6-4) produced by the core is designed to be similar to other CAEN VME modules to simplify event decoding by the DAQ and users. GEO is an identifier

of the card location inside the VME crate and must be configured by the user. CRATE denotes the number of VME crate in the measurement system and is also configured by the user.  $N_DETECTOR_PULSES$  is the number of detector pulses detected by the system starting at the end of the previous event. The coarse event timestamp is typically configured to 1  $\mu$ s period and the HIT\_TIME period is always 5 ns, with the first hit having a time of zero.

| Header                                              |                                |      |      |       |       |          |          |     |            |      |     |     |      |    |          |     |    |     |                 |     |    |          |     |   |   |   |   |

|-----------------------------------------------------|--------------------------------|------|------|-------|-------|----------|----------|-----|------------|------|-----|-----|------|----|----------|-----|----|-----|-----------------|-----|----|----------|-----|---|---|---|---|

| 31 30 29 28 27                                      | 26                             | 25   | 24   | 23 3  | 2 21  | 20       | 19       | 12  | 17         | 16   | 15  | 14  | 12   | 1  | 2 11     | 10  | q  | 8   | 7               | 6   | Ī  | 5        | 4   | 3 | 2 | 1 | 0 |

|                                                     |                                | 1    |      | 23    |       |          |          |     | <b>-</b> / | 10   | 13  |     | 13   | -  | <u> </u> | 10  |    |     |                 |     |    | <i>-</i> | _   | , |   | _ | U |

| GEO[40]                                             | 0                              | 1    | 0    |       |       |          | [7       |     |            |      |     |     |      |    |          |     | UF | 11/ | <del>1</del> _2 | IZE |    |          |     |   |   |   |   |

| Data size is th                                     |                                | eng  | th ( | of th | e ev  | ent      | with     | าดน | ıt h       | ea   | der | ar  | d fo | 00 | ter.     |     |    |     |                 |     |    |          |     |   |   |   |   |

| Coarse Event T                                      | _                              |      |      |       |       |          |          |     |            |      |     |     |      |    |          |     |    |     |                 |     |    |          |     |   |   |   |   |

| 31 30 29 28 27                                      | 26                             | 25   | 24   | 23    | 22 21 | 20       | 19       | 18  | 17         | 16   | 15  | 14  | 13   | 1  | 2 11     | 10  | 9  | 8   | 7               | 6   |    | 5        | 4   | 3 | 2 | 1 | 0 |

| GEO[40]                                             | 0                              | 0    | 0    |       |       | 0x       | 02       |     |            |      |     |     |      |    |          |     | Т  | S_  | LO              | W   |    |          |     |   |   |   |   |

| GEO[40]                                             | 0                              | 0    | 0    |       |       | 0x       | 03       |     |            |      |     |     |      |    |          |     | Т  | S_  | HIG             | ìΗ  |    |          |     |   |   |   |   |

|                                                     |                                |      |      |       |       |          |          |     |            |      |     |     |      |    |          |     |    |     |                 |     |    |          |     |   |   |   |   |

| Detector pulses                                     | Detector pulses since last IRQ |      |      |       |       |          |          |     |            |      |     |     |      |    |          |     |    |     |                 |     |    |          |     |   |   |   |   |

| 31 30 29 28 27                                      |                                |      |      |       |       | 20       | 19       | 18  | 17         | 16   | 15  | 14  | 13   | 1  | 2 11     | 10  | 9  | 8   | 7               | 6   |    | 5        | 4   | 3 | 2 | 1 | 0 |

| GEO[40]                                             | 0                              |      | 0    |       | ı     | 0x       |          |     |            |      |     |     |      |    |          | DE  |    | TC  | R               | IMI | Pι | JLS      | SES |   |   |   |   |

| Reset after th                                      | e e                            | nd   | of a | a su  | cess  | ful d    | coin     | cid | end        | ce v | win | do  | w.   |    |          |     |    |     |                 |     |    |          |     |   |   |   |   |

|                                                     |                                |      |      |       |       |          |          |     |            |      |     |     |      |    |          |     |    |     |                 |     |    |          |     |   |   |   |   |

| Event data x N                                      |                                |      |      |       |       |          |          |     |            |      |     |     |      |    |          |     |    |     |                 |     |    |          |     |   |   |   |   |

| 31 30 29 28 27                                      | 26                             | 25   | 24   | 23 2  | 22 21 | 20       | 19       | 18  | 17         | 16   | 15  | 14  | 13   | 1  | 2 11     | 10  | 9  | 8   | 7               | 6   |    | 5        | 4   | 3 | 2 | 1 | 0 |

| GEO[40]                                             | 0                              | 0    | 0    |       |       | 0x       |          |     |            |      |     |     |      | 1= |          |     |    |     | TIN             | ИF  |    | - 1      |     |   |   |   | _ |

| 020[:::0]                                           |                                |      | _    |       |       | <u> </u> | <u> </u> | PΔ  | тт         | FRI  | N 3 | 1 _ | - N  |    |          |     |    | ··- |                 |     |    |          |     |   |   |   |   |

|                                                     | PATTERN 31 – 0                 |      |      |       |       |          |          |     |            |      |     |     |      |    |          |     |    |     |                 |     |    |          |     |   |   |   |   |

| PATTERN 63 – 32 Repeated as many times as required. |                                |      |      |       |       |          |          |     |            |      |     |     |      |    |          |     |    |     |                 |     |    |          |     |   |   |   |   |

| Repeated as r                                       | mar                            | ny t | ıme  | es as | requ  | ııre     | a.       |     |            |      |     |     |      |    |          |     |    |     |                 |     |    |          |     |   |   |   |   |

|                                                     |                                |      |      |       |       |          |          |     |            |      |     |     |      |    |          |     |    |     |                 |     |    |          |     |   |   |   |   |

| Footer                                              |                                |      |      |       |       |          |          |     |            |      |     |     |      |    |          |     |    |     |                 |     |    |          |     |   |   |   |   |

| 31 30 29 28 27                                      | 26                             | 25   | 24   | 23    | 22 21 | 20       | 19       | 18  | 17         | 16   | 15  | 14  | 13   | 1  | 2 11     | 10  | 9  | 8   | 7               | 6   |    | 5        | 4   | 3 | 2 | 1 | 0 |

| GEO[40]                                             | 1                              | 0    | 0    |       |       |          |          |     |            |      |     | EV  | EN.  | Т  | CNT      | [23 | 01 |     |                 |     |    |          |     |   |   |   |   |

Table 6-4 Coincidence master event bit structure

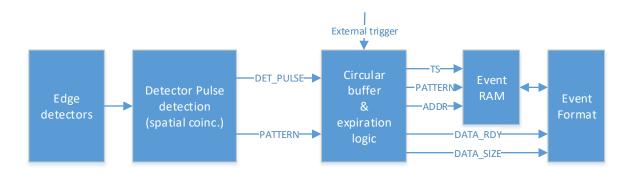

#### 6.4.2 Pattern recorder core

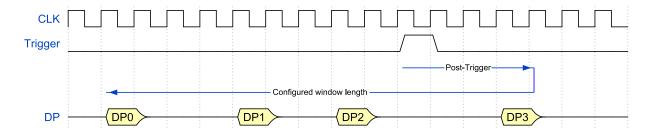

Pulse pattern recorder core is designed to record events around given point of time, such is the case when registering events from active veto detectors. It samples inputs using 5 ns clock and continuously records Detector Pulses into a circular buffer. Pulses which are over configured numerical limit or are too old are removed. After an external trigger signal is received an event is generated.

Figure 6-13 Pattern recorder core schematics

Figure 6-14 Pattern recorder event example

## 6.4.2.1 Pattern recorder core event format

| Header                              |       |     |      |                                         | 1 1        |                                  |          | 1 1     |     |    |          |      |      |       |   |   |   |   |

|-------------------------------------|-------|-----|------|-----------------------------------------|------------|----------------------------------|----------|---------|-----|----|----------|------|------|-------|---|---|---|---|

| 31 30 29 28 27                      | 26    | 25  | 24   | 23 22 21                                | 20 19 18   | <b>3</b>   <b>17</b>   <b>16</b> | 15 14 1  | 3 12 11 | 10  | 9  | 8        | 7 6  | 5    | 5 4   | 3 | 2 | 1 | 0 |

| GEO[40]                             | 0     | 1   | 0    | CR                                      | ATE[70]    | ]                                |          |         |     | DA | TA_      | SIZE |      |       |   |   |   |   |

| Data size is th                     | ne le | eng | th ( | of the eve                              | ent witho  | ut hea                           | der and  | footer. |     |    |          |      |      |       |   |   |   |   |

| <b>Coarse Event T</b>               | S     |     |      |                                         |            |                                  |          |         |     |    |          |      |      |       |   |   |   |   |

| 31 30 29 28 27                      | 26    | 25  | 24   | 23 22 21                                | 20 19 18   | 3 17 16                          | 15 14 1  | 3 12 11 | 10  | 9  | 8 7      | 7 6  | 5    | 5 4   | 3 | 2 | 1 | 0 |

| GEO[40]                             | 0     | 0   | 0    |                                         | 0x02       |                                  |          |         |     | TS | S_LC     | W    |      |       |   |   |   |   |

| GEO[40]                             | 0     | 0   | 0    |                                         | 0x03       |                                  |          |         |     | TS | _HI      | GH   |      |       |   |   |   |   |

|                                     |       |     |      |                                         |            |                                  | •        |         |     |    | _        |      |      |       |   |   |   |   |

| <b>Detector pulse</b>               | s siı | nce | las  | t IRQ                                   |            |                                  |          |         |     |    |          |      |      |       |   |   |   |   |

| 31 30 29 28 27                      |       |     |      |                                         | 20 19 18   | 3 17 16                          | 15 14 1  | 3 12 11 | 10  | 9  | 8 7      | 7 6  | 5    | 5 4   | 3 | 2 | 1 | 0 |

| GEO[40]                             | 0     |     | 0    |                                         | 0x04       |                                  |          |         | DET |    | OR       | IM   | PU   | LSE   | S |   |   |   |

| Reset after th                      | ne e  | nd  | of a | success                                 | ful coinci | dence                            | window   |         |     |    |          |      |      |       |   |   |   |   |

|                                     |       |     |      |                                         |            |                                  |          |         |     |    |          |      |      |       |   |   |   |   |

| Event data x N                      |       |     |      |                                         |            |                                  |          |         |     |    |          |      |      |       |   |   |   |   |

| 31 30 29 28 27                      | 26    | 25  | 24   | 23 22 21                                | 20 19 18   | 3 17 16                          | 15 14 1  | 3 12 11 | 10  | 9  | 8 7      | 7 6  | 5    | 5 4   | 3 | 2 | 1 | 0 |

| GEO[40]                             | 0     | 0   | 0    | - · · · · · · · · · · · · · · · · · · · | 0x01       |                                  |          |         |     |    | T TI     | ME   |      |       |   |   |   |   |

|                                     |       |     |      |                                         | P          | ATTER                            | N 31 – ( | )       |     |    | _        |      |      |       |   |   |   |   |

| PATTERN 63 – 32                     |       |     |      |                                         |            |                                  |          |         |     |    |          |      |      |       |   |   |   |   |

| Repeated as many times as required. |       |     |      |                                         |            |                                  |          |         |     |    |          |      |      |       |   |   |   |   |

|                                     |       | , . |      |                                         |            |                                  |          |         |     |    |          |      |      |       |   |   |   |   |

| Footer                              |       |     |      |                                         |            |                                  |          |         |     |    |          |      |      |       |   |   |   |   |

| 31 30 29 28 27                      | 26    | 25  | 24   | 23 22 21                                | 20 19 18   | 3 17 16                          | 15 14 1  | 3 12 11 | 10  | 9  | 8 7      | 7 6  | . [5 | 5 4   | 3 | 2 | 1 | 0 |

| GEO[40]                             | 1     | 0   | 0    | <b></b>                                 | -0         | -11-0                            |          | NT CNT  |     | _  | <u> </u> |      |      | -   " |   | - | _ |   |

Table 6-5 Coincidence master event bit structure

## 6.5 Gate generator core

It is useful to be able to generate artificial pulses of given structure for DAQ testing purposes. The gate generator outputs groups of pulses in a repeated window. After specified number of cycles, an IRQ can be generated. Each channel produces one pulse of specified duration relative to the start of the window in 5 ns steps. After each cycle, this offset can be either incremented or decremented and such adjustment be kept for given number of cycles. The gate generator core is useful for hardware in the loop testing of systems, including testing of various race conditions.

## 6.6 Firmware resource usage

Table 6-7 shows the Cyclone I FPGA resource usage for different variants of the firmware.

| Firmware ID | Description          |

|-------------|----------------------|

| QDCM        | Coincidence firmware |

| MPPC        | Pattern recorder     |

| GGEN        | Pattern generator    |

| NECL        | NIM->ECL translator  |

| ECLN        | ECL->NIM translator  |

Table 6-6 Firmware ID codes

| Firmware ID | Logical element usage | Memory usage [bits] |

|-------------|-----------------------|---------------------|

| QDCM        | 7524                  | 28 672              |

| MPPC        | 7692                  | 98 304              |

| GGEN        | 17833                 | 8192                |

| NECL        | 168                   | 0                   |

| ECLN        | 170                   | 0                   |

Table 6-7 Firmware resource usage

## 7 S<sup>3</sup> software coincidence analyzer

The spectrometer for the S<sup>3</sup> detector is based on the CAEN 64 channel 12-bit 62.5 MSPS V1740 VME Digitizer (Described in 5.2.5). The V1740 is configured in a self-triggering mode where rising edge on any input triggers simultaneous sampling of all enabled channels. The data is stored in an internal event buffers, IRQ is generated and read out by a PC running the NWVME DAQ software by Zdenek Hons [21]. Captured events are stored on the hard drive together with a system UNIX timestamp.

As part of this thesis, the SwCoinc application for data analysis was created by the author of this thesis. Its design requirements were:

- implement the inverse beta decay search algorithm

- Ability to process offline and online data from the DAQ and oscilloscopes

- online data reduction (coincidence, filtering)

- online data visualization

- ROOT file data output

The software framework has been written in C++ and uses the CERN ROOT framework for data visualization.

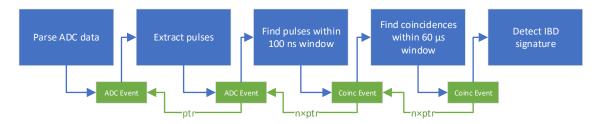

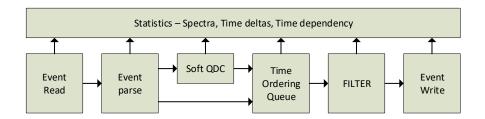

The description of the final inverse beta decay search algorithm implementation can be seen on Figure 7-1. The blue rectangles represent processes and green data. At the start of the processing is the raw ADC data file and at the end is a data structure containing coincidences of a group of pulses with likely IBD candidate detector events.

Figure 7-1 SwCoinc data flow

### 7.1 SwCoinc software description

#### 7.1.1 Data input

The SwCoinc framework reads VME crate events created by the Hons DAQ and LeCroy oscilloscope TRC wave traces and supports offline and online processing.

In the offline mode, a directory or a file is specified as an argument on the command line and the application recursively scans the directories for registered file extensions and ZIP archives containing them. One archive or one directory is defined as a single data acquisition (run). The files are sorted using a regular expression according to their extensions – the VME files have format DDMMYY:HHMMSS- $n_0$ .vme\_r, where n is the file sequence number, and the LeCroy TRC files  $Cx_y$ .TRC, where x is the oscilloscope input channel with y-th acquisition. Separate sets are created for each input channel.

In the online mode, only VME DAQ is supported and the application takes the path to the VME DAQ binary as an argument and monitors the /proc file system using the Linux inotify facility to detect whether it is running. If found, the /proc/pid/fd directory is scanned for the location of its log file. The VME log file is parsed to detect the state of the DAQ and possible file names of an active run.

The input data files are parsed into the Event class structure. Each *Event* contains aligned ADC samples from all active input channels and the timestamp. When segmented oscilloscope files are read, first *Event* contains first acquisition from all input channel files.

#### 7.1.2 Data analysis

Events are processed through Analyzer, a vector of Filters. The framework contains two analyzers – ADCPrinter and SCube. ADCPrinter outputs every a trace of ADC Events to a separate PNG file. The SCube analyzer implements the spatial and temporal coincidences to detect reactor antineutrinos.

#### 7.1.3 Data visualization

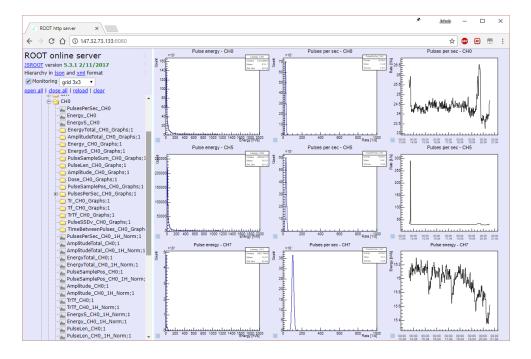

The coincidence software contains graphing classes based on ROOT's TH1 and TGraph. The visualization classes automatically create histograms for individual channels with correct names and axes and graphs of tracked variables depending on time (such as system load, pulses per second). After data processing is done, all graphs and histograms are saved as PNG files to output directory and as well as a ROOT data file.

Online monitoring uses the embedded HTTP ROOT server, which allows online access to open ROOT files via the JSROOT interface (Figure 7-2).

Figure 7-2 JSROOT web interface

#### 7.1.4 Command and control

The JSROOT interface allows starting and stopping of NWVME. The SwCoinc connects to the control interface of the DAQ and issues the start/stop command.

## 7.2 Analyzer software architecture

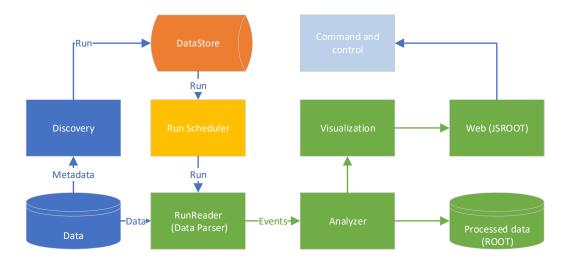

SwCoinc program structure is shown on Figure 7-3. Different colors represent separate processing threads which communicate through asynchronous message queues.

Figure 7-3 SwCoinc architecture

## 7.3 Analyzer software class overview

This chapter describes the most important C++ classes in the SwCoinc system.

#### 7.3.1 Config

A global singleton class accessible via the GLOBALS macro holding configuration of the SwCoinc system. The configuration can be set via command line arguments and an XML configuration file.

#### 7.3.2 Log

Uses the boost::log classes to allow logging of system events to console, a file or JSROOT console. There are six logging levels supported by – fatal, error, warning, info, debug and trace and each output channel can be set to a different severity level.

#### 7.3.3 RootServer

Starts and stops the ROOT HTTP server. To allow interaction between the JSROOT interface and SwCoinc, it was necessary to use the ROOT's embedded LLVM compiler. A C++ statement with a functional pointer to required SwCoinc function is compiled using the LLVM compiler which can then called by the JSROOT.

#### 7.3.4 IThread

Derivable interface class implementing C++11 std::thread. Each thread executes lambda expressions from a message FIFO in an event loop. The messages are used for inter-thread communication. It also provides the Sync method thread synchronization based on the std::future and std::promise. Listing 7-3 shows part of the implementation detail and Listing 7-3 exemplifies how the message passing is used within the SwCoinc application.

Listing 7-2 Partial IThread implementation

```

class DSScheduler : public IThread {...}

void DSScheduler::ScheduleTask(RunTask task) {

auto msg = [this, task = std::move(task) ]() mutable

{

task.runreader->Execute(task.run, m_DataSink);

};

m_msgQueue.Write(std::move(msg));

}

```

Listing 7-3 Asynchronous message passing use example

#### 7.3.5 DataStore

This class keeps track of all data sources and Run instances. It is executed in a separate thread. Spawns the Discoverer and Scheduler threads. Routes messages between the data source discovery thread and scheduling threads.

#### 7.3.6 Scheduler

The scheduler sequentially executes available Runs by creating an instance of a RunReader. For each run a new thread is created. In the future, it should be possible to extend the scheduler to be able to run multiple tasks concurrently. However, at this time ROOT is not completely thread-safe and causes issues whenever one ROOT file is accessed by multiple threads.

#### 7.3.7 Event

The Event class contains measurement data which is processed through the system. The parsers transform raw source data into an instance of this class. Listing 6-1 shows the declaration of this class.

```

bool hasADC = false;

bool hasPulse = false;

bool hasCoincidence = false;

bool hasVMECrate = false;

int CoincidenceOrder = 0; // depth of coincidences

int MergedEvents = 0; // number of overlapped ADC trigger windows merged

int MergeDelta = 0; // time delta of overlapped triggers

int CrateEventPos = 0; // position of event inside the crate event

PulseEventData Pulse; // Energy, from Pulse Extractor

VMECrateData VME; // TS of start and stop of IRQ handler

std::map<int, EventChannelData> ChannelData; // ADC data

std::vector<std::shared ptr<Event>> CoincidenceData; // events in coinc

int PeakPulseAmplitude();

bool hasCoincidenceChannels(const std::vector<int>& channels);

bool CoincidenceChannelsEqualTo(const std::vector<int>& channels);

bool hasCoincidenceMap(const std::vector<std::vector<int>>& map);

};

```

Listing 7-4 The Event class

#### 7.3.7.1 VMECrateData

Instance of this class is created for each VME crate event and contains Unix timestamps of the beginning and the end of a single VME IRQ handling.

#### 7.3.7.2 ADCEventData

Contains V1740 event data, both raw ADC samples, calculated sample voltages, trigger threshold, trigger polarity and the sampling period.

#### 7.3.7.3 PulseEventData

The PulseExtractor filter creates a new Event with PulseEventData filled. Such Event keeps pointer to the original ADC Event.

#### 7.3.7.4 CoincidenceData

Event output by the Coincidence filter contains a vector of all Events which are in a defined coincidence window. The CoincidenceOrder member variable holds the level of nesting

#### 7.3.8 DataSource

Interface base class for classes which originate Events. Implements overridable virtual methods listed in Table 6-1. Any class which instantiates a DataSource should call the SetSink() method to set the sink of the source.

| Method    | Time of call by implementing method     |

|-----------|-----------------------------------------|

| DataStart | At the start of data processing         |

| RunStart  | At the start of a single run processing |

| SendEvent | When an Event to be send is generated |

|-----------|---------------------------------------|

| RunEnd    | At the end of a single run processing |

| DataEnd   | At the end of data processing         |

Table 7-1 DataSource interface method

#### 7.3.9 DataSink

Interface base class for classes which process Events. Methods are listed in Table 7-2. The update method is called to re-generate online monitoring graphs every one real time second.

| Method       | Time of call by a DataSource                         |

|--------------|------------------------------------------------------|

| DataStart    | At the start of data processing                      |

| RunStart     | At the start of a single run processing              |

| ProcessEvent | When an Event to be send to be processed             |

| RunEnd       | At the end of a single run processing                |

| DataEnd      | At the end of data processing                        |

| Update       | Periodically, should run time intensive calculations |

Table 7-2 DataSink interface method

#### 7.3.10 Filter and LambdaFilter

The Filter class is a base for classes which act both as a sink and a source. Inheriti from both DataSource and DataSink. The LambdaFilter is a filter which takes a C++ lambda as a parameter to be applied on each Event.

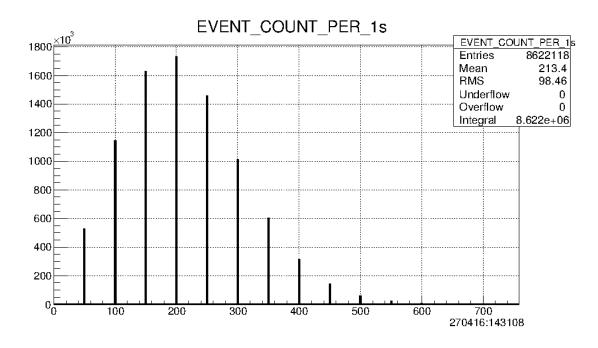

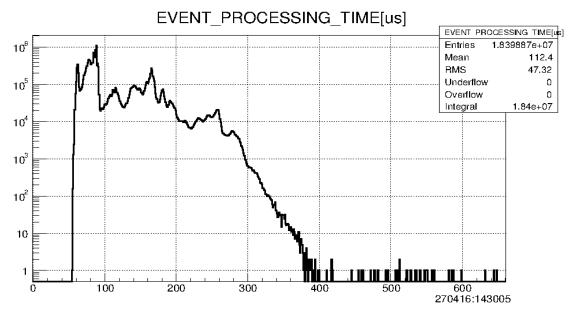

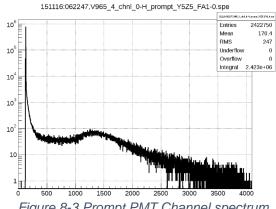

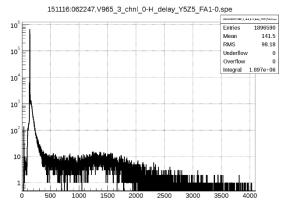

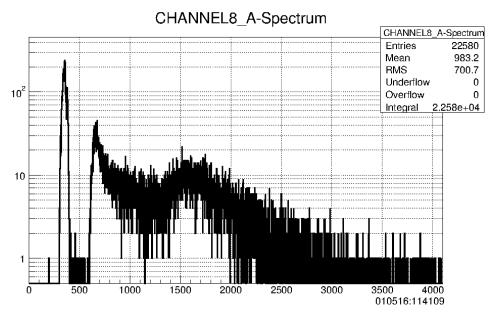

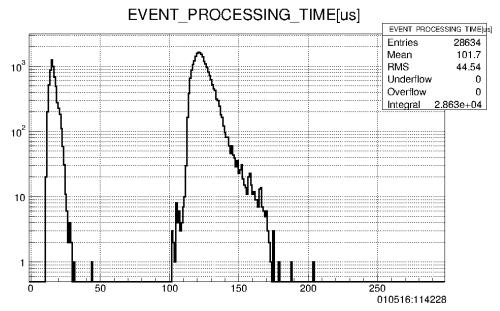

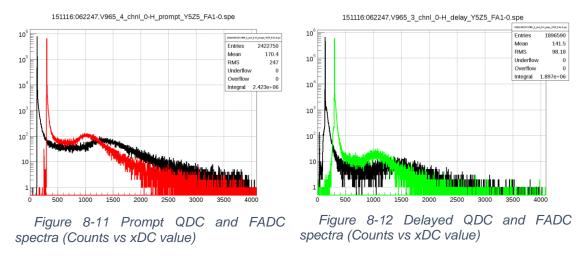

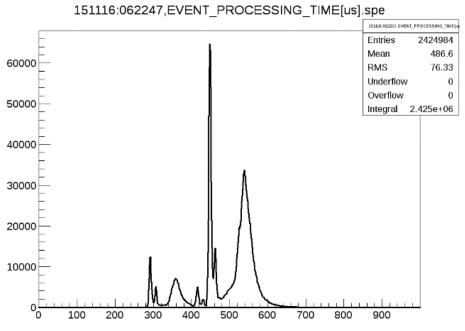

#### 7.3.11 PulseExtractor